# User's Manual

Version 0.5 Sept. 23, 2005

# **Preliminary**

Copyright 2005 NEXIA DEVICE CO., LTD. , New Name of Mobile Doctor Co., Ltd., All rights reserved.

NEXIA DEVICE CO., LTD. Confidential and Proprietary

The information in this document is proprietary to NEXIA DEVICE CO., LTD.

The information shall not be used, copied, reproduced or disclosed in whole or in part without written consent of NEXIA DEVICE CO., LTD.

The information can be changed by NEXIA DEVICE CO., LTD. without notice for its purpose and revision

# **Preliminary**

# **Digital Audio SoC**

## 1. Table of Contents

| 1. | TABLE OF CONTENTS2                                                        |

|----|---------------------------------------------------------------------------|

| 2. | PRODUCT OVERVIEW3                                                         |

|    | 2.1. FEATURES                                                             |

|    | 2.2. TARGET APPLICATION                                                   |

|    | 2.3. BLOCK DIAGRAM OF NX5850                                              |

| 3. | SIGNAL DESCRIPTIONS                                                       |

| 4. | SYSTEM BOOT                                                               |

|    | 4.1. BOOT MODE                                                            |

|    | 4.2. THE BOOTING PROCEDURE OF NOR FLASH MEMORY                            |

|    | 4.3. THE BOOTING PROCEDURE OF RAM                                         |

|    | 4.4. BOOT MODE CONTROL REGISTER                                           |

| 5. | SYSTEM CLOCK CONTROL                                                      |

|    | 5.1. CLOCK SOURCE CONTROL REGISTER                                        |

| 6. | MCU                                                                       |

|    | 6.1. FEATURES                                                             |

|    | 6.2. Address Map                                                          |

| 7. | NOR FLASH/LCD INTERFACE                                                   |

|    | 7.1. Nor Flash/LCD Interface Register                                     |

| 8. | SYSTEM CONTROL BLOCK                                                      |

|    | 8.1. System Control Block Register                                        |

| 9. | USB CONTROLLER3                                                           |

|    | 9.1. USB2.0 Full Speed Function Controller                                |

|    | 9.1.1. Operation                                                          |

|    | 9.1.2. Signaling Levels3                                                  |

|    | 9.1.3. Bit Encoding3                                                      |

|    | 9.1.4. Field Formats                                                      |

|    | 9.1.5. Packet Formats3                                                    |

|    | 9.1.6. Transaction Formats                                                |

|    | 9.1.7. UDC Device Requests                                                |

|    | 9.1.8. USB Device Application                                             |

|    | 9.2. USB1.1 Host Controller                                               |

|    | 9.3. USB Control Register                                                 |

| 10 | ). DMA CONTROLLER 3                                                       |

|    | 10.1. DMA OPERATION                                                       |

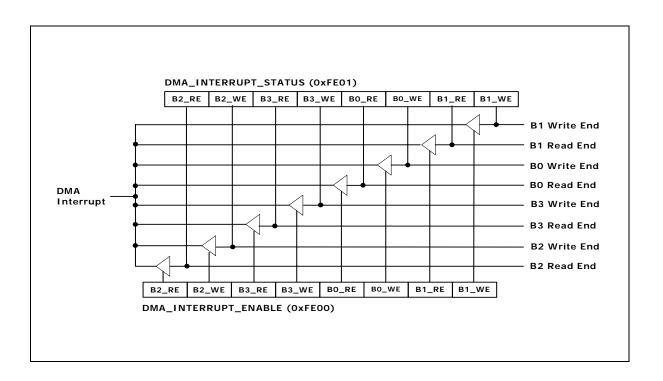

|    | 10.1.1. Full Interrupt Communication of DMA Controller 51                 |

|    | 10.1.2. A Example for the Full-Interrupt Routine of the DMA Controller 53 |

|    | 10.1.3. Half-Interrupt communication of DMA Controller 53                 |

|    | 10.1.4. A Example for the Half-Interrupt Routine of the DMA Controller 53 |

|    | 10.1.5. The Polling Communication of the DMA Controller 53                |

# **Digital Audio SoC**

# **Preliminary**

| 10.1.6. A Example for the Polling Routine of the DMA Controller | 54  |

|-----------------------------------------------------------------|-----|

| 10.2. DMA CONTROL REGISGER                                      | 54  |

| 11. MMC/SD CARD INTERFACE                                       | 68  |

| 11.1. MMC/SD Interface                                          | 68  |

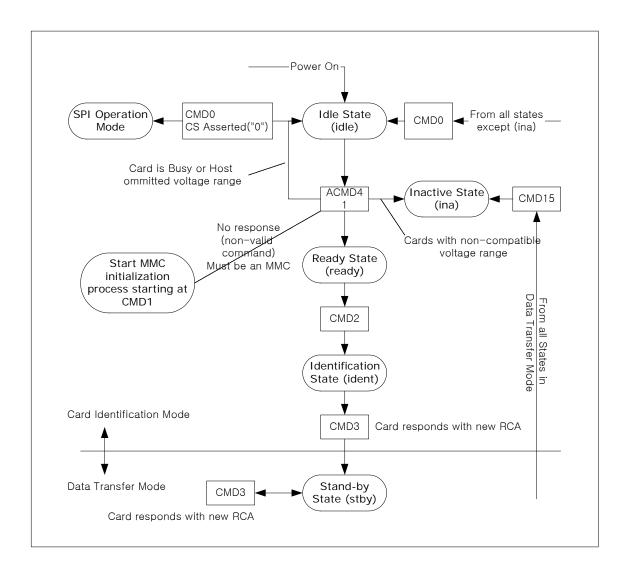

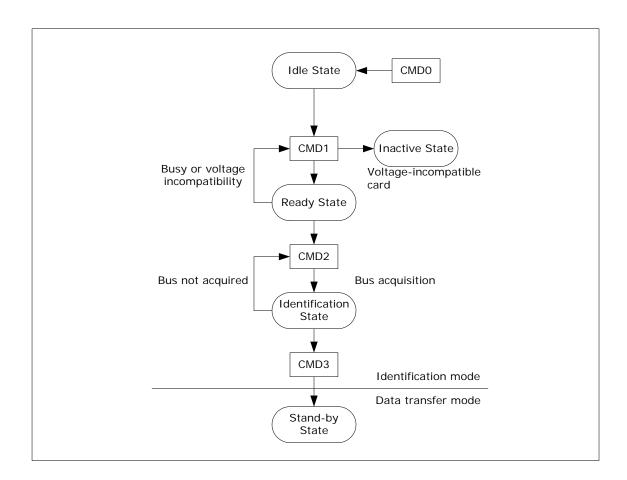

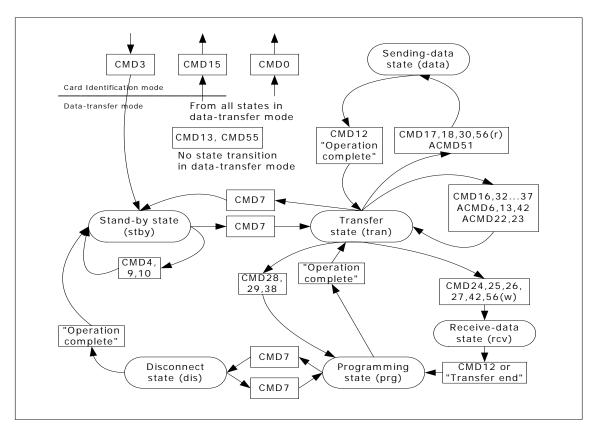

| 11.2. Initialization of MMC and SD Card                         | 68  |

| 11.3. MMC/SD Card Control Register                              | 72  |

| 12. NAND CONTROLLER                                             | 78  |

| 12.1. NAND FLASH INTERFACE                                      | 78  |

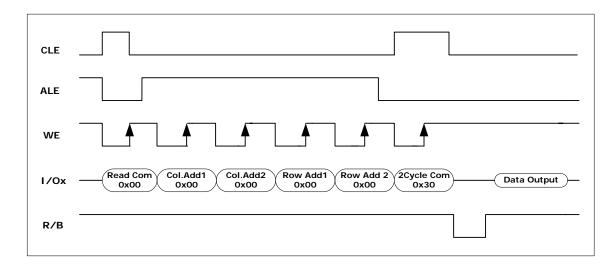

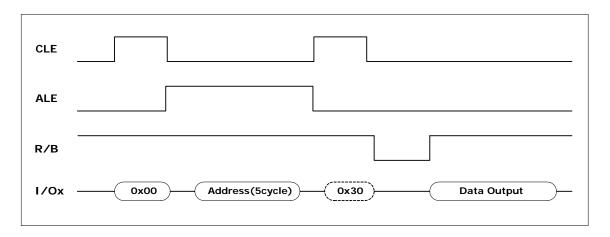

| 12.1.1. Reading data from NAND Flash Memory                     | 78  |

| 12.1.2. Example for NAND Flash Read                             | 79  |

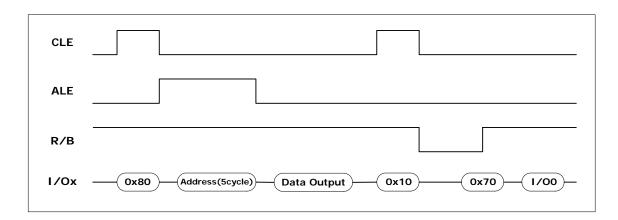

| 12.1.3. Writing data to NAND Flash memory                       | 80  |

| 12.1.4. Example for NAND Flash Write                            | 81  |

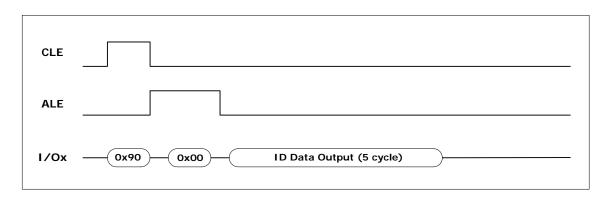

| 12.1.5. Read ID Operation                                       | 82  |

| 12.1.6. Example for NAND Flash ID Read                          | 82  |

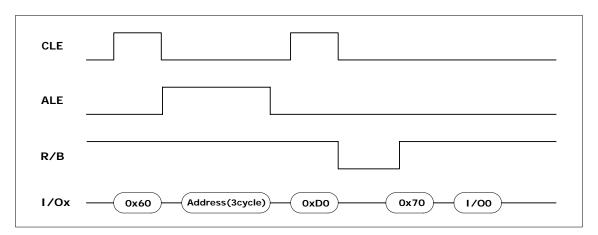

| 12.1.7. Block Erase Operation of NAND Flash                     | 83  |

| 12.1.8. Example for Block Erase of NAND Flash                   | 83  |

| 12.2. NAND FLASH CONTROL REGISTER                               | 87  |

| 13. DRM CONTROLLER                                              | 93  |

| 13.1. DRM OPERATION                                             | 93  |

| 13.2. DRM Control Register                                      | 93  |

| 14. HARDWIRED AUDIO/VOICE ENGINE                                | 96  |

| 14.1. Overview                                                  | 96  |

| 14.2. MP3 ENCODING CONTROL REGISTER                             | 97  |

| 14.3. Audio CODEC Interface                                     | 100 |

| 14.4. SRS/WOW CONTROL                                           | 101 |

| 14.5. MPEG1/2 ENCODER CONTROL                                   | 103 |

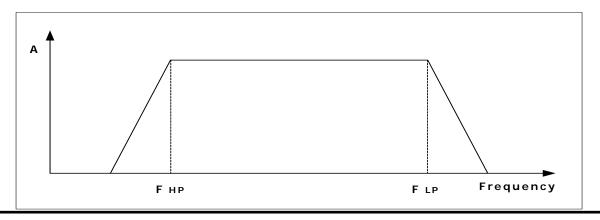

| 14.6. FILTER                                                    | 104 |

| 14.7. MUTE DETECT FUNCTION                                      | 106 |

| 14.8. Sound Effect Control                                      | 109 |

| 14.9. Reading The Header Information                            | 116 |

| 15. RTC (REAL TIME CLOCK)                                       | 126 |

| 15.1. RTC Power Supply & Clock                                  | 126 |

| 15.2. RTC CONTROL REGISTER                                      | 126 |

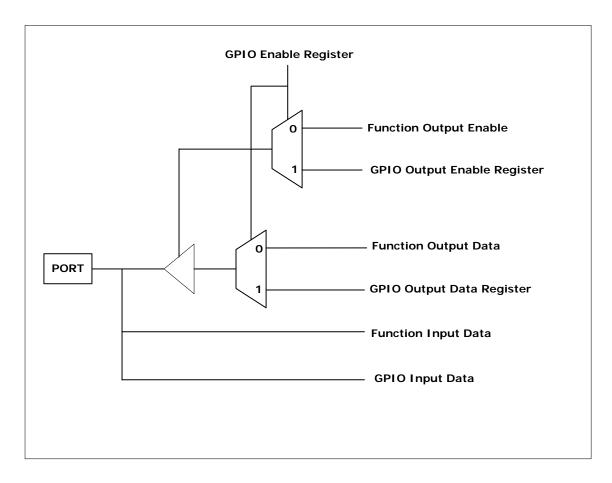

| 16. GPIO (GENERAL PURPOSE INPUT OUTPUT)                         | 130 |

| 16.1. GPIO CONTROL REGISTER                                     | 130 |

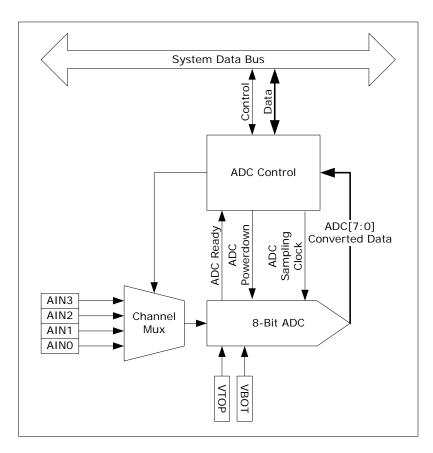

| 17. ADC (ANALOG-TO-DIGITAL CONVERTER)                           | 138 |

| 18.1. ADC CONTROL REGISTER                                      | 139 |

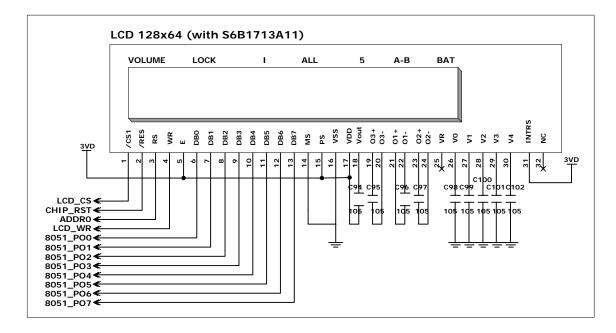

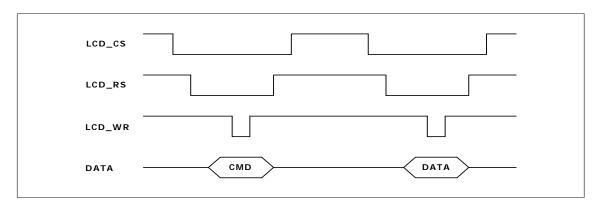

| 18. LCD CONTROL                                                 | 142 |

| 18.1. Parallel (8080 mode) Interface (8bit)                     | 142 |

| 18.2 Serial Interface                                           | 143 |

| 18.2.1. Serial Interface Control Register                       | 143 |

# **Digital Audio SoC**

# Preliminary

| 19. PACKAGE                              | 145 |

|------------------------------------------|-----|

| 20. ELECTRICAL CHARACTERISTICS           | 147 |

| 20.1 Absolute Maximum Ratings            | 147 |

| 21.2 RECOMMENDED OPERATING CONDITIONS    | 147 |

| 20.3 ELECTRICAL CHARACTERISTICS FOR PLLS | 148 |

| 20.3.1 Recommended Operating Conditions  | 148 |

| 20.3.2 DC Electrical Characteristics     | 148 |

| 20.3.3 AC Electrical Characteristics     | 148 |

| 20.4 ELECTRICAL CHARACTERISTICS FOR ADC  | 149 |

| 20.4.1 Recommended Operating Conditions  | 149 |

| 20.4.2 DC Electrical Characteristics     | 149 |

| 20.4.3 AC Electrical Characteristics     | 149 |

| 21 PIN DESCRIPTION                       | 151 |

# 2. Product Overview

#### 2. Product Overview

NX5850 audio application SoC provides a high-performance audio processing for MP3 and WMA applications such as the digital audio players, PDAs, voice recorders, MP3 recorders, and cell phones.

Based on the Hardwired Logic Design, NX5850 offers the superior power efficiency coupled with high performance. The SoC integrates the DMA used for the audio data processing, the USB 2.0 device and USB1.1 host used for downloading and uploading audio data from/to a PC and a comprehensive set of peripherals to support some medias such as MMCs, SDs, Flash memories and etc.

#### 2.1. Features

#### **General Features**

- Operating Voltage: 3.3V (I/O) / 1.8V (Core)

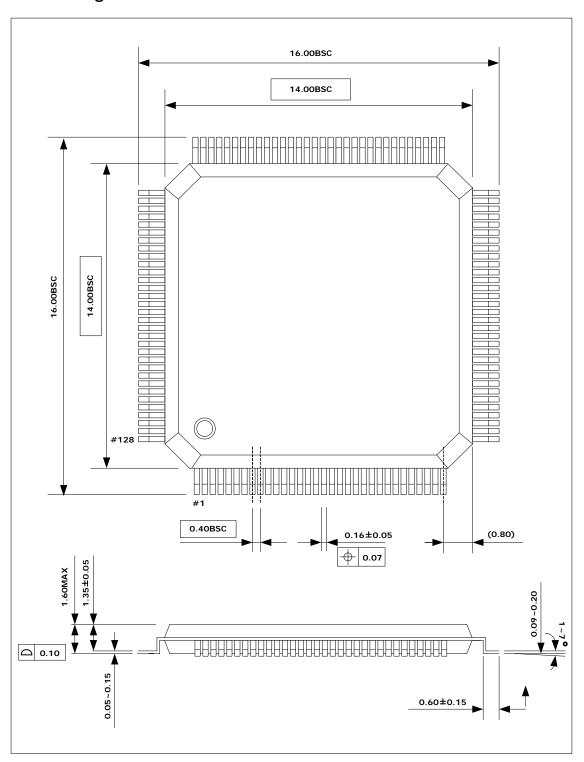

- Package : 128LQFP (14mm x 14mm)

- Low Frequency and Ultra Low Power Operating

- Crystal Oscillator: 12MHz

- Program ROM: External NOR/NAND Flash

- Update Firmware through USB Ports

- LCD Interface : Serial/Parallel/DMA

- Audio Effect Control

- srs wow 3D effects

- 10 band equalizer

- Bypass / Volume / Bass / Treble / Normal / Mute

- Includes RTC(Real Time Clock)

- Includes MP3 Decoder, MP3 Encoder, WMA Decoder, DMA, USB, GPIOs

- Media Interfaces and 8bit RISC MCU of 8051 Compatible

#### Audio/Voice CODEC

#### MP3 Full Function for Encoding and Decoding

- Includes MP3 decoder and MP3 encoder

- MP3 Encoder for MPEG1/2 Audio Layer 3 and MP3 Decoder for MPEG1/2/2.5 Audio Layer 3

- Includes CODEC for Voice (8 ~ 160Kbps)

- Real Time Processing of Encoding/Decoding in MP3 Format

- Based on the fully Hardwired Logic Design for Power Efficiency

#### **WMA Decoder Full function**

- Based on the fully Hardwired Logic Design for Power Efficiency

- · Includes WMA decoder

- Real time processing of decoding in WMA format

- · Based on the fully hard-wired logic design for power efficiency

- WMA DRM version 9 (PD-DRM) is supported

#### **DMA Control**

• Structure to handle memories for DMA with high performance

#### **USB 2.0 Full Speed**

• The embedded USB2.0 full speed controller for device function

## **USB 1.1 Host Controller**

- The embedded USB 1.1 controller for host function

- NX5850 supports one port of USB host interface that has the following features such as OHCI

#### Media Interfaces

- SMC and NAND Flash (with ECC)

- MMC, SD, CF, NAND, SRAM

# **Digital Audio SoC**

### **Analog Part**

- Includes 4 channel ADC for Voice Recording, Battery Detection and Key Function

- Includes PLL

#### **WMA DRM**

• WMA DRM Version 9 (PD-DRM) is supported

Equalizer 10 Bands SRS WOW 3D Sounds Real Time Clock

## 2.2. Target Application

#### MP3/WMA Player and Voice Recorder

- Audio Applications to handle Audio Function for the Portable, Home and Car categories

- Voice Applications to handle Voice Recording Functions

- Others such as Education System, Mobile phone, PDA and etc.

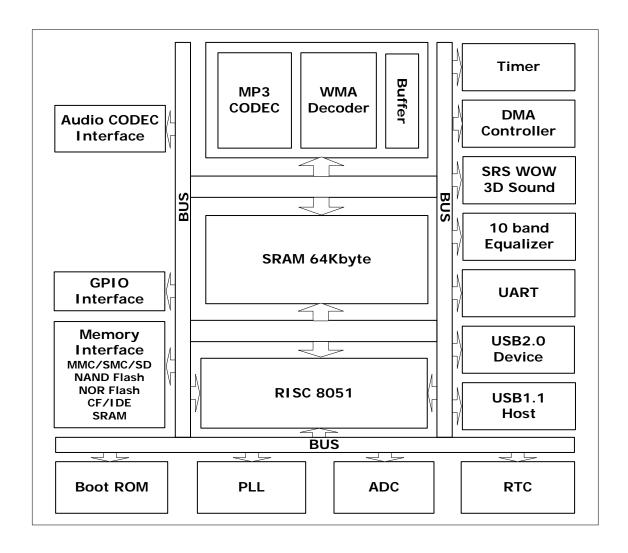

## 2.3. Block Diagram of NX5850

Figure 1. The Block Diagram of NX5850

# 3. Signal Descriptions

**Digital Audio SoC**

## 3. Signal Descriptions

Table 1. 8051 Ports Signal Description

| Signal<br>Name | Туре | Description                                        | Pin<br>Number           |

|----------------|------|----------------------------------------------------|-------------------------|

| P1             | 1/0  | 8051 Port 1                                        | 35,34,33,32,31,30,29,28 |

| [7:0]          |      | P1 is an 8-bit bidirectional I/O port.             |                         |

| P2             | 1/0  | 8051 Port 2                                        | 82,73,72,83,69,24,70,71 |

| [7:0]          | 1/0  | P2 is an 8-bit bidirectional I/O port.             | 02,73,72,03,07,24,70,71 |

| P3             | 1/0  | 8051 Port 3                                        | 4E 44 42 42 41 40 20 20 |

| [7:0]          | 1/0  | P3 is an 8-bit bidirectional I/O port.             | 45,44,43,42,41,40,39,38 |

| MADDR          |      | 8051 Lower Address [7:0]                           |                         |

|                | 1/0  | These bits are latched output of 8051 Port 0 in    | 84,85,86,87,10,11,12,13 |

| [7:0]          |      | NX5850 .                                           |                         |

| UADDR          |      | Nor flash/RAM Upper Address [21:16]                |                         |

|                | 1/0  | These bits can be used when external NOR flash/RAM | 79,78,77,76,75,74       |

| [5:0]          |      | program code data exceeds 64Kbyte.                 |                         |

**Table 2. System Signal Description**

| Signal<br>Name | Туре | Description                  | Pin<br>Number |

|----------------|------|------------------------------|---------------|

| RESETn         | I    | Chip Reset                   | 126           |

| TM             | ı    | Chip Test Mode Selection pin | 4             |

**Table 3. General Purpose IO Description**

| Signal<br>Name | Туре                                       | Description                           | Pin<br>Number                |

|----------------|--------------------------------------------|---------------------------------------|------------------------------|

| GPI00          | 1/0                                        | GPIO0 [7:0] (PSEN,ALE,GPIO5~GPIO0)    | 25,46,79,78,77,76,75,74      |

| [7:0]          | 1/0                                        | General purpose input/output group 0  | 25,40,79,78,77,70,75,74      |

| GPIO1          | 1/0                                        | GPIO1 [4:0] (DM,DP,F_RNB,LCD,XRM)     | 9,8,88,128,127               |

| [7:0]          | 1/0                                        | General purpose input/output group 1  | 7,0,00,120,127               |

| GPIO2          | 1/0                                        | GPIO2 [7:0] (ADDR[7:0])               | 84,85,86,87,10,11,12,13      |

| [7:0]          | 1/0                                        | General purpose input/output group 2  | 84,85,86,87,10,11,12,13      |

| GPIO3          | 1/0                                        | GPIO3 [7:0] (LCDDATA[7:0]=P0[7:0])    | 23,22,21,20,19,16,15,14      |

| [7:0]          | 1/0                                        | General purpose input/output group 3  | 23,22,21,20,14,10,13,14      |

| GPIO4          | 1/0                                        | GPIO4 [5:0] (P1[7:0])                 | 35,34,33,32,31,30,29,28      |

| [5:0]          | 170                                        | General purpose input/output group 4  | 33,34,33,32,31,30,27,20      |

| GPIO5          | 1/0                                        | GPI05 [6:0] (P2[7:0])                 | 82,73,72,83,69,24,70,71      |

| [6:0]          | 1/0                                        | General purpose input/output group 5  | 02,73,72,03,07,24,70,71      |

| GPIO6          | 1/0                                        | GPIO6 [7:0] (P3[7:0])                 | 45,44,43,42,41,40,39,38      |

| [7:0]          | 170                                        | General purpose input/output group 6  | 45,44,45,42,41,40,57,50      |

| GPIO7          | 1/0                                        | GPIO7 [7:0] (FD [7:0]/NRA[15:8])      | 89,90,91,92,93,94,95,96      |

| [7:0]          | 17                                         | General purpose input/output group 7  | 07,70,71,72,73,74,73,70      |

| GPIO8          | 1/0                                        | GPIO8 [7:0] (NorLCD_D[15:8])          | 56,55,54,53,52,51,50,49      |

| [7:0]          | 17                                         | General purpose input/output group 8  | 30,33,34,33,32,31,30,47      |

| GPIO9          | 1 1/0 1 (MCMD MDAT MCLK MCK SCK CCK SDL SD |                                       |                              |

| [7:0]          |                                            |                                       | 66,65,64,63,62,61,60,59      |

| [7.0]          |                                            | General purpose input/output group 9  |                              |

| GPIO10         |                                            | GPIO10 [7:0]                          |                              |

| [7:0]          | 1/0                                        | (CE3,CE2,CE1,CE0,FCLE,FALE,FWEN,FREN) | 97,98,99,100,103,104,105,106 |

| [,]            |                                            | General purpose input/output group 10 |                              |

**Table 4. Analog Signal Description**

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                          | Pin<br>Number   |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| AIN<br>[3:0]   | AI   | Analog Input  These pins are analog input for internal ADC, which converts the analog input signal into 8-bit binary digital codes at a maximum conversion rate of 1MSPS with 10Mhz clock.                                                                           | 118,119,120,121 |

| VBOT           | ΑI   | Reference Bottom  Bottom level of the ADC. The pin is connected to analog ground.                                                                                                                                                                                    | 122             |

| VTOP           | AI   | Reference Top  The analog input is single-ended type and the range is from VTOP to VBOT. The analog input voltage follows reference voltage range fundamentally. So, if you want to alter into the another input range, you should change the voltage value of VTOP. | 123             |

### Table 5. External Memory Interface (MMC) Signal Description

| Signal<br>Name | Туре | Description         | Pin<br>Number |

|----------------|------|---------------------|---------------|

| MMC<br>CLK     | 1/0  | MMC Clock           | 64            |

| MMC<br>DATA    | 1/0  | MMC Data 0          | 65            |

| MMC<br>CMD     | 1/0  | MMC Command         | 66            |

| MMC<br>DATA1   | 1/0  | GPIOO<br>MMC DATA 1 | 74            |

| MMC<br>DATA2   | 1/0  | GPIO1<br>MMC DATA 2 | 75            |

| MMC<br>DATA3   | 1/0  | GPIO2<br>MMC DATA 3 | 76            |

## Table 6. External Nand Flash Memory Interface Signal Description

| Signal<br>Name | Туре | Description               | Pin<br>Number           |

|----------------|------|---------------------------|-------------------------|

| FCEN3          | 1/0  | NAND Chip Enable 3        | 97                      |

| FCEN2          | 1/0  | NAND Chip Enable 2        | 98                      |

| FCEN1          | 1/0  | NAND Chip Enable 1        | 99                      |

| FCENO          | 1/0  | NAND Chip Enable 0        | 100                     |

| FCLE           | 1/0  | NAND Command Latch Enable | 103                     |

| FALE           | 1/0  | NAND Address Latch Enable | 104                     |

| FWEN           | 1/0  | NAND Write Enable Strobe  | 105                     |

| FREN           | 1/0  | NAND Read Enable Strobe   | 106                     |

| FRNB           | 1/0  | NAND Ready and Busy       | 88                      |

| FIO<br>[7:0]   | I/O  | NAND I/O [7:0]            | 89,90,91,92,93,94,95,96 |

Table 7. External Nor Flash Memory Interface Signal Description

| Signal<br>Name | Туре | Description                  | Pin<br>Number           |

|----------------|------|------------------------------|-------------------------|

| NRCS1          | 1/0  | NOR Chip Enable 1 (F_CE1)    | 99                      |

| NRCS0          | 1/0  | NOR Chip Enable 0 (F_CE0)    | 100                     |

| NWR            | 1/0  | NOR Write Data Strobe (P3.6) | 44                      |

| NRD            | 1/0  | NOR Read Data Strobe (P3.7)  | 45                      |

| ADDR<br>[7:0]  | 0    | NOR Address [7:0]            | 84,85,86,87,10,11,12,13 |

| ADDR<br>[15:8] | 0    | NOR Address [15:8]           | 89,90,91,92,93,94,95,96 |

# **Digital Audio SoC**

| ADDR<br>[21:16] | 0   | NOR Address[21:16]              | 79,78,77,76,75,74       |

|-----------------|-----|---------------------------------|-------------------------|

| DATA<br>[7:0]   | 1/0 | NOR Data[7:0] (P0[7:0])         | 23,22,21,20,19,16,15,14 |

| DATA<br>[15:8]  | 1/0 | NOR Data[15:8] (NorLCD_D[15:8]) | 56,55,54,53,52,51,50,49 |

### Table 8. RTC Interface (Real Time Clock) Signal Description

| Signal<br>Name     | Туре                                                                                                       | Description                                                                                                                                                                                                                                                    |         |

|--------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| RTCIN              | I                                                                                                          | Real Time Crystal Oscillator Input  To use the Real Time Clock counter, a 32.768KHz crystal oscillator is connected this pin. If an external oscillator is used, its output is connected to this pin. RTCIN is the clock source for internal RTC counter only. |         |

| RTCOUT             | Real Time Crystal Oscillator Output  To use the Real Time Clock counter, a 32 768KHz crystal oscillator is |                                                                                                                                                                                                                                                                | 2       |

| 1.8V<br>RTC<br>VDD | Р                                                                                                          | Independent Power for RTC Timer only                                                                                                                                                                                                                           | 115     |

| 3.3V<br>RTC<br>VDD | Р                                                                                                          | Independent Power for RTC Oscillator                                                                                                                                                                                                                           | 125     |

| RTC<br>GND         | Р                                                                                                          | Power Ground                                                                                                                                                                                                                                                   | 114,124 |

## Table 9. Boot Selection and Firmware Update Signal Description

| Signal<br>Name     | Туре | Description                | Pin<br>Number |

|--------------------|------|----------------------------|---------------|

| Firmware<br>Update | 1    | Firmware Update            | 3             |

| Boot<br>Selection  | I    | Nor/Nand Flash Memory Boot | 5             |

## **Table 10. Audio Codec Interface Signal Description**

| Signal<br>Name | Туре | Description               | Pin<br>Number |

|----------------|------|---------------------------|---------------|

| ACMCK          | 1/0  | Audio Codec Master Clock  | 63            |

| ACSCK          | 1/0  | Audio Codec Sample Clock  | 62            |

| ACCCK          | 1/0  | Audio Codec Channel Clock | 61            |

| ACSDI          | 1/0  | Audio Codec Data Input    | 60            |

| ACSDO          | 1/0  | Audio Codec Data Output   | 59            |

### **Table 11. Clock Signal Description**

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                    | Pin<br>Number |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| XIN            | ı    | System Clock Crystal Oscillator Input  To use the internal oscillator, a crystal/resonator circuit is connected this pin. If an external oscillator is used, its output is connected to this pin. XIN is the clock source for internal timing. | 109           |

| XOUT           | 0    | System Clock Crystal Oscillator Output  To use the internal oscillator, a crystal/resonator circuit is connected to this pin. If an external oscillator is used, leave X2 unconnected.                                                         | 110           |

Table 12. USB Interface Signal Description

| Signal<br>Name | Туре | Description            | Pin<br>Number |

|----------------|------|------------------------|---------------|

| USBDP          | 1/0  | USB Positive Data Line | 8             |

| USBDM          | 1/0  | USB Negative Data Line | 9             |

**Table 13. LCD Interface Signal Description**

| Si       | gnal   | Тур | Description             | Pin                     |

|----------|--------|-----|-------------------------|-------------------------|

| Name     |        | е   | Description             | Number                  |

|          | LCDNCE | 1/0 | LCD Module Chip Enable  | 128                     |

|          | LCDRS  | 1/0 | LCD Module Mode Select  | 13                      |

| Parallel | LCDNWR | 1/0 | LCD Module Write Enable | 44                      |

| Mode     | LCDIO  | 1/0 | LCD Module Data [7:0]   | 23,22,21,20,19,16,15,14 |

|          | [15:0] | 1/0 | LCD Module Data [15:8]  | 56,55,54,53,52,51,50,49 |

|          | LCDNRD | 1/0 | LCD Module Read Enable  | 45                      |

**Table 14. Power Signal Description**

| Cianal         | 1    |                                                   | Pin    |

|----------------|------|---------------------------------------------------|--------|

| Signal<br>Name | Туре | Description                                       | Number |

| VDDe6          | Р    | Analog I/O Power for Digital Part                 | 6      |

| GNDe7          | G    | Analog I/O Ground for Digital Part                | 7      |

| VDDe17         | Р    | Digital I/O Power for Digital Part                | 17     |

| GNDe18         | G    | Digital I/O Ground for Digital Part               | 18     |

| VDDi26         | Р    | Digital Core Power for Digital Part 1.8V          | 26     |

| GNDi27         | G    | Digital Core Ground for Digital Part              | 27     |

| GNDe36         | G    | Digital I/O Ground for Digital Part               | 36     |

| VDDe37         | Р    | Digital I/O Power for Digital Part                | 37     |

| GNDi47         | G    | Digital Core Ground for Digital Part              | 47     |

| VDDi48         | Р    | Digital Core Power for Digital Part 1.8V          | 48     |

| GNDe57         | G    | Digital I/O Ground for Digital Part               | 57     |

| VDDe58         | Р    | Digital I/O Power for Digital Part                | 58     |

| GNDi67         | G    | Digital Core Ground for Digital Part              | 67     |

| VDDi68         | Р    | Digital Core Power for Digital Part 1.8V          | 68     |

| GNDe80         | G    | Digital I/O Ground for Digital Part               | 80     |

| VDDe81         | Р    | Digital I/O Power for Digital Part                | 81     |

| VDDi101        | Р    | Digital Core Power for Digital Part 1.8V          | 101    |

| GNDi102        | G    | Digital Core Ground for Digital Part              | 102    |

| VDDe107        | Р    | Digital I/O Power for Digital Part                | 107    |

| GNDe108        | G    | Digital I/O Ground for Digital Part               | 108    |

| AVDD111        | Р    | Analog Power for Analog Part 1.8V                 | 111    |

| AGND112        | G    | Analog Ground for Analog Part                     | 112    |

| AGND114        | G    | Digital Ground for Real Time Clock Timer Part     | 114    |

| AVDD115        | Р    | Digital Power for Real Time Clock Timer Part 1.8V | 115    |

| AGND116        | G    | Digital Ground                                    | 116    |

| NC             | NC   | NC                                                | 117    |

| GND124         | G    | Digital Ground for Real Time Clock Part           | 124    |

| VDD125         | Р    | Digital Power for Real time Clock Part            | 125    |

# 4. System Boot

## 4. System Boot

#### 4.1. Boot Mode

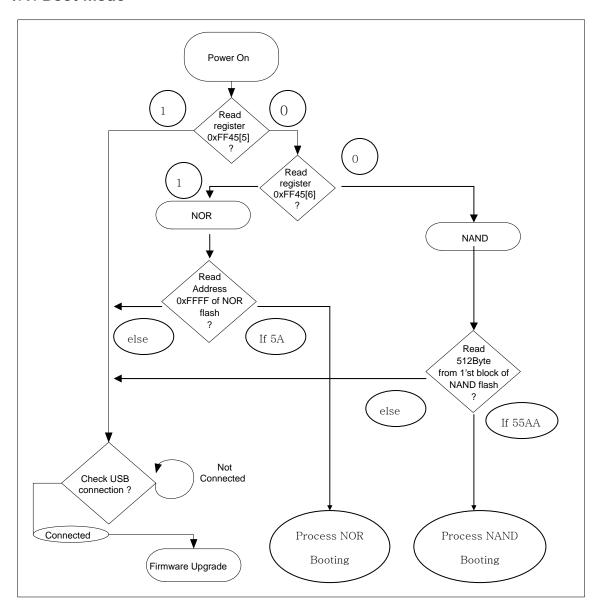

Figure 2. Boot Mode Selection flow chart

Figure 2. shows the selection procedure of the Boot Mode. There are three boot modes such as NOR Flash Memory, Nand Flash Memory and firmware update booting, and the modes are selected by the pin number 3 and 5 on NX5850. User can determine a boot mode of three with any state combination of pin number 3 and 5. But This data sheet recommends pin number 3 as firmware update mode pin and pin number 5 as Nor Flash Memory boot mode pin. If pin 3 is high it's firmware update mode, if pin3 is low normal booting mode. If pin5 is high it's Nor Flash memory booting mode and if pin5 is low it's Nand Flash memory boot mode. Figure 2 is the boot flow chart in this recommend case.

#### NOR Flash Boot Mode

The program is executed with the program code on the NOR Flash. The NOR Flash(EEPROM) can be upgraded.

# **Digital Audio SoC**

### NAND Flash Boot Mode

A program is executed with the program code on the NAND flash. The NAND flash can be upgraded.

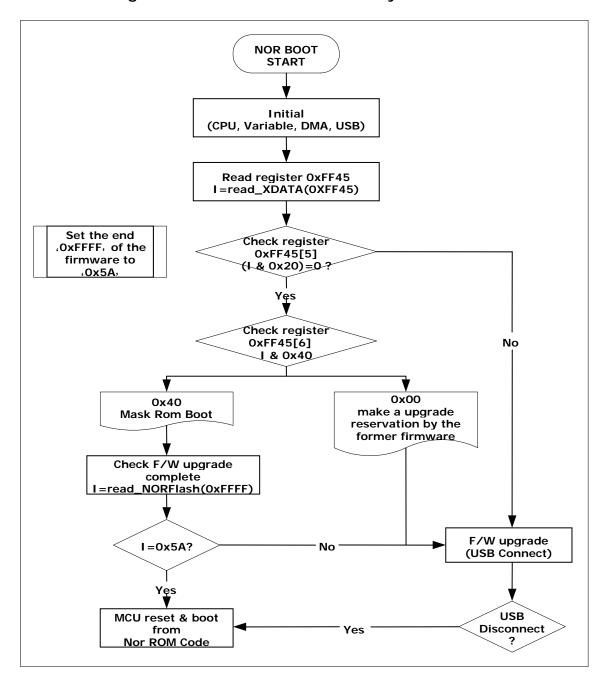

## 4.2. The Booting Procedure of NOR Flash Memory

Figure 3. The Flow Chart for NOR Flash Boot Mode

Figure 3. shows the boot mode flow of the NOR flash. The status of the NorFlash/T3(External pin) can be read at the register '0xFF45[6]'.

When executing the internal ROM boot by resetting, the NorFlash/T3 has low normally, and when upgrading a firmware by a hardware switch, executing the mask ROM boot, NorFlash/T3 has high. When the NorFlash/T3 is low, it need to check if the firmware in NOR flash is available or not, and then if the firmware is available, get the NOR flash booting to be perform without the firmware upgrade. The way that checks whether the firmware in the NOR flash is available or not is that checks whether the last address '0xFFFF' of the NOR flash is '0x5A' or not. According to this, the firmware to write into the NOR flash have to be 64Kbyte, which is the NOR flash capacity with putting '0x5A' at the last address '0xFFFF' when converting Hex to Binary. The maximum size of the firmware is the size that is lack of 1 byte. The other warning is the firmware upgrade that uses the mask ROM boot code. It is that only operates with the firmware upgrade PC application.

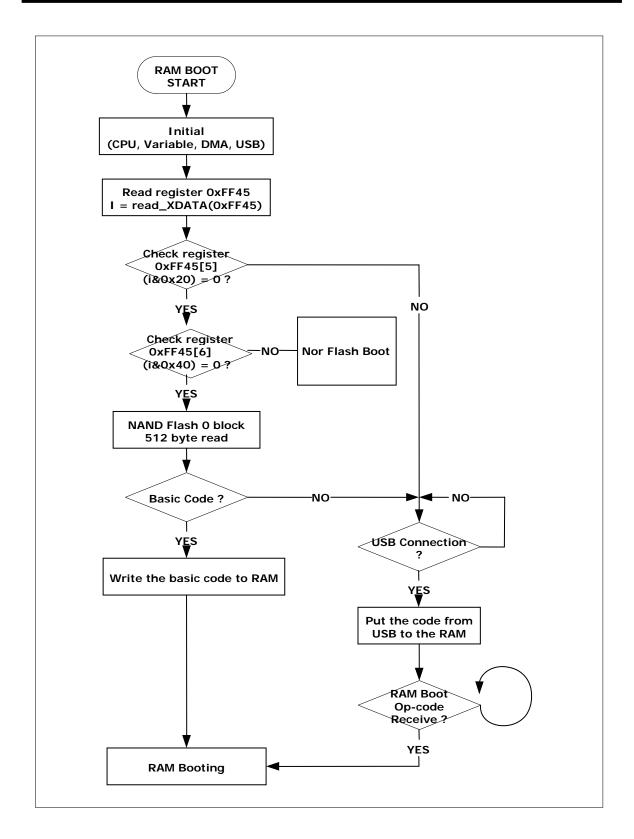

#### 4.3. The Booting Procedure of NAND flash

The followings are a procedure to find a basic code after reading the block 0 of the NAND flash.

Table 15. The contents of Block 0 of the NAND Flash

|        | 0x0  | 0x1  | 0x2  | 0x3  | 0x4  | 0x5  | 0x6  | 0x7  | 0x8  | 0x9  | ОхА | ОхВ | OxC  | 0xD  | OxE  | 0xF |

|--------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|-----|

| 0x0000 | 0x55 | OxAA | 0x08 | 0x00 | 0x04 | 0x00 | 0x00 | 0x00 | 0x01 | 0x00 | Rev | Rev | 0x30 | 0x01 | 0x02 |     |

| 0x0010 |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

| 0x0020 |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

| 0x0030 |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

| •      |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

| •      |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

| 0x01F0 |      |      |      |      |      |      |      |      |      |      |     |     |      |      |      |     |

- 1)  $0x00 \sim 0x01$  : Signature = '0x55AA'.

- 2)  $0x02 \sim 0x03$  : Sector Size = '0x0800' (2048 byte).

- 3) 0x04: Address Number = '0x04' (4 Addresses).

- 4) 0x05: Flash Memory Command = '0x00' (Read Command).

- 5) 0x06 ~ 0x0B: Address Area = '0x0A ~ 0x0B' is reserved because Address is four as above.

- 6) 0x0C : This is used when the second cycle command is needed. The command '0x30' means the read command on the second cycle. If you need not the second cycle, '0xFF' should be written.

- 7) 0x0D : Shows the number of sectors of basic code to read.

- 8) 0x0E: Row Address Number.

- 9) 0x0F ~ 0x01FF : Reserved Area

Figure 4. Flow Chart for RAM Boot Mode

#### A Explanation for Advance Flash Memory of 128Mbyte (Table 15)

If the signature of Table 15. don't has a value of 0x55AA, the booting mode goes to the firmware upgrade mode because it judges that there is no basic code. This means that being in a waiting mode for getting data from the USB like as looking at the flow chart of Figure 4. The code for the upgrading the firmware is put on the RAM, and the code for the firmware upgrade is executed as performing a RAM booting when a OP-code is transferred to notice that the code download is done. If there is the signature, judges that a basic code is exist and executes like follows:

Figure 5. The procedure of Basic code1

The Table 15. shows the configuration of the block 0, which has a location for the basic code on the NAND flash.

As seeing the Table 15, the address '0x05' has 0x00(read command), and the '0x04' has 0x04(the number of valid address). The four valid addresses are '00, 00, 01, 00'(0x06 ~ 0x09) and they are written into the NAND flash data IO line. The 0x0C is the second cycle command, and the value is 0x30(read command). To doing the RAM booting, read the 2048 byte(1 sector) from the NAND flash to NX5850 by the DMA transfer. And then the system is reset and the booting code executes on the RAM. If the 0x0D is '2', the booting code executes after reading the second sector. We have to know the start position of the row address in the address '0x06 ~ 0x0B' because the some kinds of NAND flashes have a different size of the column address. So, the 0x0E has 0x02, which is noticed the start of the row address.

### 4.4. Boot Mode Control Register

Table 16. Boot Mode Register Map

| Function                            | Address<br>(Hex) | Туре             | Reset       | Description                      |

|-------------------------------------|------------------|------------------|-------------|----------------------------------|

| BOOT_MODE_SELECT<br>FIRMWARE UPDATE | 0xff45           | R[6:0]<br>W[4:0] | 8,PXXX00000 | BOOT_MODE_SELECT FIRMWARE UPDATE |

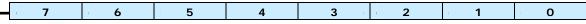

#### Boot Mode Select (BOOT\_MODE\_SELECT, 0xFF45) : Read[6:0]/Write[4:0]

| 7 | 6         | 5        | 4      | 3      | 2     | 1   | 0   |

|---|-----------|----------|--------|--------|-------|-----|-----|

|   | Nor Flash | Firmware | USB DM | USB DP | F_R/B | LCD | XRM |

|   | Boot      | Update   |        |        |       |     |     |

## **Digital Audio SoC**

This register is used to set the boot mode.

Nor Flash Boot: This bit is used to check the Nor Flash Memory booting mode. Read only GPI.

- 0: Perform the Nand Flash Memory Boot.

- 1 : Perform the Nor Flash Memory Boot.

Firmware Update: This bit is used to check the Firmware Update mode. Read only GPI.

- 0: Nand or Nor Flash Memory Boot.

- 1 : Perform the firmware upgrade from USB.

**USB DM**: This bit is used as GPIO Read/Write at the time of GPIO mode.

USB DP: This bit is used as GPIO Read/Write at the time of GPIO mode.

$\textbf{F\_R/B}:$  This bit is used as GPIO Read/Write at the time of GPIO mode.

**LCD**: This bit is used as GPIO Read/Write at the time of GPIO mode.

XRM: This bit is used as GPIO Read/Write at the time of GPIO mode.

# 5. System Clock Control

**Digital Audio SoC**

## 5. System Clock Control

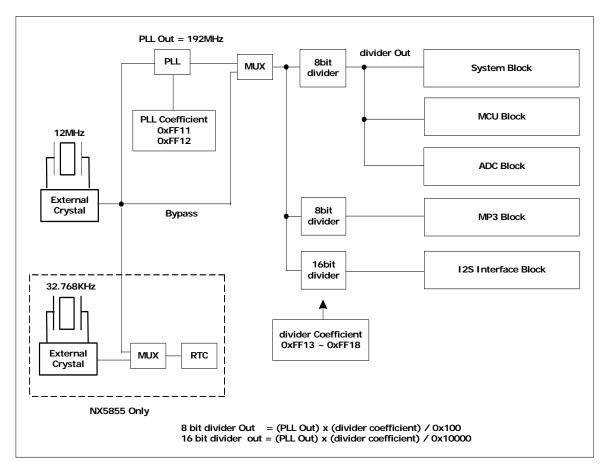

NX5850 has one PLL with external Crystal Oscillator input and system internal clock source is supplied by PLL output through several divider to each function block. Each function block clock is divider output frequency which is PLL output frequency divided by divider value. User sets PLL coefficient register value for PLL out put frequency control and sets divider register value to determine divider output frequency.

Figure 6. The Diagram of the Clock Distribution

#### 5.1. Clock Source Control Register

Table 17. Clock source control Register Map (P2 = 0xFF)

| Function                   | Address<br>(Hex) | Туре | Reset | Description                             |

|----------------------------|------------------|------|-------|-----------------------------------------|

| CLOCK_SOURCE_CONTROL       | 0x04             | R/W  | 0x07  | Clock Source Control                    |

| DEFAULT_COEFFICIENT_ENABLE | 0x10             | R/W  | 0x1f  | Use Default PLL and divider coefficient |

| PLL_COEFFICIENT_LO         | 0x11             | R/W  | 0x00  | Controls PLL Output Frequency           |

| PLL_COEFFICIENT_HI         | 0x12             | R/W  | 0x00  |                                         |

| DIVIDER_COEFFICIENT_VALUE  | 0x13<br>~0x18    | R/W  | 0x00  | Controls divider Output Frequency       |

## **Digital Audio SoC**

| AUDIO_CLOCK_STATUS | 0x19 | RO | 0x0F | Audio Clock Status Register |  |

|--------------------|------|----|------|-----------------------------|--|

|--------------------|------|----|------|-----------------------------|--|

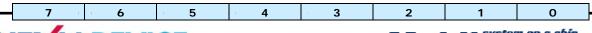

#### Clock Source Control (CLOCK\_SOURCE\_CONTROL, 0xFF04): Read/Write, 0x07

| 7 | 6 | 5        | 4 | 3 | 2       | 1        | 0        |

|---|---|----------|---|---|---------|----------|----------|

|   |   | Reserved |   |   | XTAL_EN | XTAL_ SE | PLL_PWDN |

#### XTAL\_EN:

0 : stops crystal oscillation.1 : starts crystal oscillation.

#### XTAL\_SE:

0 : use pll output clock as internal.1 : use crystal clock as internal clock.

#### PLL\_PWDN:

0 : starts pll operation.1 : stops pll operation.

#### Default Coefficient Enable (DEFAULT\_COEFFICIENT\_ENABLE, 0xFF10): Read/Write, 0x1f

| 7 | 6        | 5 | 4        | 3       | 2       | 1        | 0       |

|---|----------|---|----------|---------|---------|----------|---------|

|   | Reserved |   | PLL_COEF | SYS_DIV | MP3_DIV | reserved | AUD_DIV |

#### PLL\_COEF:

0 : use register(0xFF11-0xFF12) value as PLL coefficient1 : use default value as PLL coefficient(0x0ABE).

#### SYS\_DIV:

**0** : use register(0xFF13) value as 8bit divider coefficient **1** : use default value as 8bit divider coefficient(0x40).

#### MP3\_DIV:

**0**: use register(0xFF14) value as 8bit divider coefficient **1**: use default value as 8bit divider coefficient(0x10).

#### reserved:

#### AUD\_DIV:

**0**: use register(0xFF17-0xFF18) value as 16bit divider coefficient

1: use default value as 16bit divider coefficient(varies depending on sampling frequency).

### $PLL\ Coefficient\ Low\ (PLL\_COEFFICIENT\_LOW,\ 0xFF11): Read/Write,\ 0x00$

| 7 | 6 | 5 | 4      | 3      | 2 | 1 | 0 |

|---|---|---|--------|--------|---|---|---|

|   |   |   | PLL_CO | EF_LOW |   |   |   |

This register is used to read/write the lower 8-bit of the 16-bit PLL Coefficient.

#### PLL Coefficient High (PLL\_COEFFICIENT\_HIGH, 0xFF12): Read/Write, 0x00

| 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|---------------|---|---|---|---|---|---|--|--|

|   | PLL_COEF_HIGH |   |   |   |   |   |   |  |  |

This register is used to read/write the upper 8-bit of the 16-bit PLL Coefficient. PII out = pII in \* (coefficient[7:0]+2) / ( (coefficient[13:8]+2)\*2^coefficient[15:14] )

#### System Divider Value (SYS\_DIVDER\_VALUE, 0xFF13) : Read/Write, 0x00

| 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------------|---|---|---|---|---|---|---|--|--|

| CVC DIV VAI   |   |   |   |   |   |   |   |  |  |

| \$15_BTV_V/\L |   |   |   |   |   |   |   |  |  |

# **Digital Audio SoC**

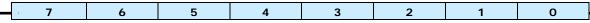

#### MP3 Divider Value (MP3\_DIVIDER\_VALUE, 0xFF14) : Read/Write, 0x00

| 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |

|---|---|---|-------|--------|---|---|---|

|   |   |   | MP3_D | IV_VAL |   |   |   |

#### Audio Divider Value Low (AUDIO\_DIVIDER\_VALUE\_LOW, 0xFF17): Read/Write, 0x00

| 7 | 6 | 5 | 4        | 3       | 2 | 1 | 0 |

|---|---|---|----------|---------|---|---|---|

|   |   |   | AUD_DIV_ | VAL_LOW |   |   |   |

This register is used to read/write the lower 16-bit of the Audio Divider Value.

#### Audio Divider Value High (AUDIO\_DIVIDER\_VALUE\_HIGH, 0xFF18) : Read/Write, 0x00

| 7 | 6 | 5 | 4        | 3        | 2 | 1 | 0 |

|---|---|---|----------|----------|---|---|---|

|   |   |   | AUD_DIV_ | VAL_HIGH |   |   |   |

This register is used to read/write the upper 16-bit of the Audio Divider Value.

#### Audio Clock Status (AUDIO\_CLOCK\_STATUS, 0xFF19): Read Only

| 7 | 6    | 5    | 4 | 3 | 2    | 1    | 0 |

|---|------|------|---|---|------|------|---|

|   | Rese | rved |   |   | AUD_ | _STA |   |

This register indicates the audio sampling frequency

: 11.025Khz : 11.025Khz : 22.05Khz **0011**: 44.1Khz

**0100**: 12Khz **0101**: 12Khz **0110**: 24Khz **0111**: 48Khz

1000 : 8Khz 1001 : 8Khz 1010 : 16Khz 1011 : 32Khz

1100 : 8Khz 1101 : 8Khz 1110 : 16Khz 1111 : 32Khz

# 6. MCU

# **Digital Audio SoC**

#### 6. MCU

CPU operating on NX5850 is similar to the general 8051 H/W structure and its operating method. Therefore, the programming method is the same to the general 8051 CPU, only to warn is to set up the controllers by the given specification to interface with respective device controller on NX5850.

#### 6.1. Features

- 8051 8-bit CPU

- General IO ports (Port 1, 2, 3)

- 64Kbyte external RAM on the chip (Compatible to data, code use)

- 256Byte internal RAM on the chip

- Two 16-bit timer/counters

- Full-duplex serial port (UART)

- Power-saving modes support

- DMA interface (Efficiency H/W interface composition)

- Event interrupt 0 (Composition to increase DMA efficiency)

### 6.2. Address Map

The following Table 18. is the address configuration for the register map by controlling the MCU.

**Table 18. Address Allocation Map**

| Address Range                 | description        | Remarks                                |

|-------------------------------|--------------------|----------------------------------------|

| 0x0000 – 0xF7FF               | Internal SRAM area | SRAM for program and data              |

| 0xF800 – 0xF8FF NOR_CTRL area |                    | Control block for LCD/NOR Flash memory |

| 0xF900 – 0xF9FF               | DRM_CTRL area      | Control block for DRM                  |

| 0xFA00 – 0xFAFF               | MP3_CTRL area      | Control block for MP3 decoder/encoder  |

| 0xFB00 – 0xFBFF               | MMC_CTRL area      | Control block for Multi Media Card     |

| 0xFC00 - 0xFCFF               | NAND_CTRL area     | Control block for NAND Flash memory    |

| 0xFD00 – 0xFDFF               | USB_CTRL area      | Control block for USB                  |

| 0xFE00 – 0xFEFF               | DMA_CTRL area      | Control block for DMA                  |

| 0xFF00 – 0xFFFF               | SYS_CTRL area      | Control block for internal system      |

# 7. Nor Flash /LCD Interface

#### 7. Nor Flash/LCD Interface

Nor Flash/LCD Interface is used for Nor Flash memory boot and parallel LCD interface control

#### 7.1. Nor Flash/LCD Interface Register

The description of control registers for Nor Flash memory interface and LCD interface.

Table 19. Nor flash / LCD interface Control Register Map (P2 = 0xF8)

| Function                 | Address<br>(Hex) | Туре | Reset | Description                      |

|--------------------------|------------------|------|-------|----------------------------------|

| NOR_DMA_INTERRUPT_ENABLE | 0x00             | R/W  | 0x00  | DMA end interrupt enable control |

| NOR_DMA_INTERRUPT_STATUS | 0x01             | R/W  | 0x00  | DMA end interrupt status control |

| NOR_STROBE_TIMING        | 0x02             | R/W  | 0x00  | NOR DMA strobe timing control    |

| NOR_CONTROL              | 0x03             | R/W  | 0x00  | NOR access type control          |

| NOR_ADDR_HI              | 0x04             | R/W  | 0x00  | NOR address high                 |

| NOR_ADDR_LO              | 0x05             | R/W  | 0x00  | NOR address low                  |

| NOR_DATA_HI              | 0x06             | R/W  | 0x00  | NOR data high                    |

| NOR_DATA_LO              | 0x07             | R/W  | 0x00  | NOR data low                     |

The method to set 20bit address for random access : use offset address 0x04, 0x05, GPIO0~GPIO5.

16bit mode read: Read data from offset address 0x07 first and then offset address 0x06.

16bit mode write: Write data to offset address 0x06 and then offset address 0x07.

8bit mode read/write: use data from/to offset address 0x07 only.

### ${\bf DMA\ End\ Interrupt\ Enable\ Control\ (NOR\_DMA\_INTERRUPT\_ENABLE,\,0xF800): Read/Write}$

| 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0      |

|---|---|---|----------|---|---|---|--------|

|   |   |   | Reserved |   |   |   | INT_EN |

$\label{eq:normalinterrupt_enable} \textbf{NOR\_DMA\_INTERRUPT\_ENABLE[7:1]}: \ \mathsf{Reserved}.$

INT\_EN: Writing each bit with 1 enables interrupt generation when each interrupt condition occurs.

#### DMA End Interrupt Status Control (NOR\_DMA\_INTERRUPT\_STATUS, 0xF801): Read/Write

| 7 | 6 | 5 | 4        | 3 | 2 | 1        | 0 |  |  |  |  |  |

|---|---|---|----------|---|---|----------|---|--|--|--|--|--|

|   |   |   | Reserved |   |   | Reserved |   |  |  |  |  |  |

$\label{eq:normalinterrupt_status} \textbf{NOR\_DMA\_INTERRUPT\_STATUS[7:1]}: \textbf{Reserved}.$

**INT\_STA**: Writing 1 clears interrupt status.

## **Digital Audio SoC**

### NOR Strobe Timing Control(NOR\_STROBE\_TIMING, 0xF802): Read/Write

| 7 | 6   | 5   | 4 | 3 | 2   | 1   | 0 |

|---|-----|-----|---|---|-----|-----|---|

|   | HI_ | LEN |   |   | LO_ | LEN |   |

This defines /RD pin and /WR pin output pulse width(defines read / write speed).

**HI\_LEN[7:4]**: Show the nor strobe timing high period length.

**LO\_LEN[3:0]**: Show the nor strobe timing Low period length.

#### NOR Flash Access Type Control(NOR\_CONTROL, 0xF803) : Read/Write

| 7 | 6    | 5    | 4 | 3      | 2       | 1      | 0      |

|---|------|------|---|--------|---------|--------|--------|

|   | Rese | rved |   | 16_MOD | ADD_INC | DMA_RD | DMA_WR |

This defines nor flash memory access type.

NOR\_CONTROL[7:4]: Reserved.

**16\_MOD**: This bit used to nor flash memory data access mode.

0 : 16bit data access mode select.

1: 8bit data access mode select.

ADD\_INC: This bit is used to continuously incremental addressing to nor flash memory.

0 : disables address increment.

1 : enables address increment.

**DMA\_RD**: This bit is used to external DMA read enable.

0 : Disabled.1 : Enabled.

**DMA\_WR**: This bit is used to external DMA write enable.

0 : Disabled.1 : Enabled.

#### NOR Flash Address High(NOR\_ADDR\_HI, 0xF804): Read/Write

| 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---|---|---|-----|------|---|---|---|

|   |   |   | ADD | R_HI |   |   |   |

This register is used to read / write the upper 8-bit of 16-bit of the NOR flash address.

#### NOR Flash Address Low(NOR\_ADDR\_LO, 0xF805) : Read/Write

| 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---|---|---|-----|------|---|---|---|

|   |   |   | ADD | R_LO |   |   |   |

This register is used to read / write the lower 8-bit of 16-bit of the NOR flash address.

#### NOR Flash Data High(NOR\_DATA\_HI, 0xF806): Read/Write

| 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---|---|---|-----|------|---|---|---|

|   | - |   | DAT | A_HI |   |   |   |

This register is used to read / write the upper 8-bit of 16-bit of the NOR flash data.

# **Digital Audio SoC**

# **Preliminary**

NOR Flash Data Low(NOR\_DATA\_LOW, 0xF807) : Read/Write

| 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|---|---|---|------|------|---|---|---|

|   |   |   | DATA | A_LO |   |   |   |

This register is used to read / write the lower 8-bit of 8-bit/16-bit of the NOR flash data.

# 8. System Control Block

## 8. System Control Block

System Control Block is for controlling interrupt to CPU, controlling reset and clock source to each function block, controlling RTC, and controlling GPIO.

## 8.1. System Control Block Register

The description of control registers for System Control Block.

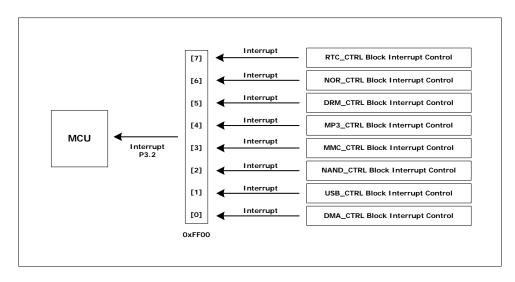

Figure 7. External Interrupt Mask to MCU

Table 20. System Control Register Map (P2 = 0xFF)

| Function                | Address<br>(Hex) | Туре | Reset | Description                           |

|-------------------------|------------------|------|-------|---------------------------------------|

| BLOCK_INTERRUPT_ENABLE  | 0x00             | R/W  | 0x00  | Each system block enable control      |

| BLOCK_INTERRUPT_STATUS  | 0x01             | RO   | -     | Each system block status read         |

| ROM_BOOT_MODE           | 0x02             | R/W  | 0x01  | ROM boot mode select                  |

| FUNCTION_BLOCK_RESET    | 0x03             | R/W  | 0x7F  | Each function block reset control     |

| NOR_HI_ADDR_ENABLE      | 0x05             | R/W  | 0x00  | Nor flash high address enable control |

| SYS_BLOCK_POWER_CONTROL | 0x06             | R/W  | 0x00  | Each system block power control       |

| MP3_BLOCK_POWER_CONTROL | 0x07             | R/W  | 0x00  | MP3 block power control               |

| DYNAMIC_POWER_CONTROL   | 0x08             | R/W  | 0x00  | Auto power-down control               |

#### System Block Interrupt Enable(BLOCK\_INTERRUPT\_ENABLE, 0xFF00): Read/Write

| 7        | 6        | 5        | 4        | 3        | 2         | 1        | 0        |

|----------|----------|----------|----------|----------|-----------|----------|----------|

| RTC_CTRL | NOR_CTRL | DRM_CTRL | MP3_CTRL | MMC_CTRL | NAND_CTRL | USB_CTRL | DMA_CTRL |

Writing each bit with 1 enables interrupt generation if each interrupt condition occurs.

RTC\_CTRL: This bit is used to RTC block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

## **Digital Audio SoC**

NOR\_CTRL: This bit is used to NOR flash or LCD interface block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

**DRM\_CTRL**: This bit is used to DRM block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

MP3\_CTRL: This bit is used to MP3 block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

MMC\_CTRL: This bit is used to MMC block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

NAND\_CTRL: This bit is used to NAND flash interface block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

USB\_CTRL: This bit is used to USB block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

$\textbf{DMA\_CTRL}:$  This bit is used to DMA block interrupt enable.

0 : interrupt disable.1 : interrupt enable.

#### System Block Interrupt Status(BLOCK\_INTERRUPT\_STATUS, 0xFF01): Read only

| 7       | 6       | 5       | 4       | 3       | 2        | 1       | 0       |

|---------|---------|---------|---------|---------|----------|---------|---------|

| RTC_STA | NOR_STA | DRM_STA | MP3_STA | MMC_STA | NAND_STA | USB_STA | DMA_STA |

Each bit indicates interrupt status of each block. And access to each block which the interrupt generated clears the corresponding bit.

RTC\_STA: This bit is used to indicates interrupt generated at the RTC block.

0: No action.

1: indicates interrupt generated.

NOR\_STA: This bit is used to indicates interrupt generated at NOR flash or LCD interface block.

0 : No action.

1 : indicates interrupt generated.

$\textbf{DRM\_STA}:$  This bit is used to indicates interrupt generated at DRM block.

0: No action.

1 : indicates interrupt generated.

MP3\_STA: This bit is used to indicates interrupt generated at MP3 block.

0 : No action.

1: indicates interrupt generated.

# **Preliminary**

## **Digital Audio SoC**

**MMC\_STA**: This bit with indicates interrupt generated at MMC block.

0: No action.

1 : indicates interrupt generated.

NAND\_STA: This bit is used to indicates interrupt generated at NAND flash block.

0 : No action

1 : indicates interrupt generated.

USB\_STA: This bit is used to indicates interrupt generated at USB block.

0 : No action.

1: indicates interrupt generated.

**DMA\_STA**: This bit is used to indicates interrupt generated at DMA block.

0: No action.

1: indicates interrupt generated.

#### Boot by ROM Mode Control(ROM\_BOOT\_MODE, 0xFF02): Read/Write

| 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0        |

|---|---|---|----------|---|---|---|----------|

|   |   |   | Reserved |   |   |   | ROM_BOOT |

If user want to reboot from RAM, user write program into RAM from boot address and the write this bit with 0. This resets CPU only and boots from RAM.

**ROM\_BOOT**: This bit is used to boot mode select.

0: RAM boot mode.

1 : ROM boot mode select. Power reset makes ROM boot mode.

#### Function Block Reset Control(FUNCTION\_BLOCK\_RESET, 0xFF03): Read/Write

| 7    | 6    | 5       | 4       | 3       | 2       | 1       | 0        |

|------|------|---------|---------|---------|---------|---------|----------|

| Rese | rved | ADC_RST | USB_RST | NOR_RST | DRM_RST | MMC_RST | NAND_RST |

Writing 0 to each bit makes corresponding function block reset.

ADC\_RST: This bit is used to ADC block reset.

0 : ADC Block reset.

1: No action.

USB\_RST: This bit is used to USB block reset.

0: USB Block reset.

1 : No action.

NOR\_RST: This bit is used to NOR block reset.

0 : NOR Block reset.

1 : No action.

**DRM\_RST**: This bit is used to DRM block reset.

0 : DRM Block reset.

1 : No action.

$\mbox{\bf MMC\_RST}$  : This bit is used to MMC block reset.

0 : MMC Block reset.

1: No action.

NAND\_RST: This bit is used to NAND flash interface block reset.

0: NAND flash interface Block reset.

1 : No action.

#### NOR flash high address enable control (NOR\_HI\_ADDR\_ENABLE, 0xFF05): Read/Write

|   | 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0      |

|---|---|---|---|----------|---|---|---|--------|

| Ī |   |   |   | Reserved |   |   |   | NOR_EN |

**NOR\_EN**: Writing 0x01 makes 0xF804(NOR flash address high register) usable and then writing NOR flash memory address[15:8] value into register 0xF804 makes NAND flash memory data pin(Fdata[7:0]) output NOR flash memory address[15:8] value.

0: No action.

1: NOR flash high address Enable.

#### System Block Power Control (SYSTEM\_BLOCK\_POWER\_CONTROL, 0xFF06): Read/Write

| 7      | 6      | 5       | 4       | 3      | 2      | 1      | 0       |

|--------|--------|---------|---------|--------|--------|--------|---------|

| RTC_PD | ADC_PD | USB0_PD | USB1_PD | NOR_PD | DRM_PD | MMC_PD | NAND_PD |

Writing 1 to each bit disables clock supply into corresponding block and results in power down of corresponding block.

RTC\_PD: This bit is used to RTC block power down.

0 : No action.

1: RTC block power down.

ADC\_PD: This bit is used to ADC block power down.

0: No action.

1 : ADC block power down.

**USBO\_PD**: This bit is used to USBO block power down.

0 : No action.

1: USB0 block power down.

**USB1\_PD**: This bit is used to USB1 block power down.

0: No action.

1: USB1 block power down.

NOR\_PD: This bit is used to NOR block power down.

0 : No action.

1 : NOR block power down.

$\textbf{DRM\_PD}$  : This bit is used to DRM block power down.

0 : No action.

1 : DRM block power down.

MMC\_PD: This bit is used to MMC block power down.

0: No action.

1 : MMC block power down.

**NAND\_PD**: This bit is used to NAND flash interface block power down.

0: No action.

# **Preliminary**

# **Digital Audio SoC**

1 : NAND flash interface block power down.

#### MP3 Block Power Control (MP3\_BLOCK\_POWER\_CONTROL, 0xFF07): Read/Write

| 7        | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|----------|---|---|--------|--------|--------|--------|--------|

| Reserved |   |   | AUD_PD | COM_PD | ENC_PD | DEC_PD | WMA_PD |

Writing 1 to each bit disables clock supply into corresponding block and results in power down of corresponding block.

AUD\_PD: This bit is used to audio block power down.

0: No action.

1 : Audio block power down.

**COM\_PD**: This bit is used to common block power down.

0: No action.

1 : Common block power down.

$\ensuremath{\textbf{ENC\_PD}}$  : This bit is used to MP3 encoder block power down.

0: No action.

1: MP3 encoder block power down.

**DEC\_PD**: This bit is used to MP3 decoder block power down.

0: No action.

1 : MP3 decoder block power down.

WMA\_PD: This bit is used to WMA decoder block power down.

0 : No action.

1 : WMA decoder block power down.

#### Auto Power Down Control (DYNAMIC\_POWER\_CONTROL, 0xFF08): Read/Write

| 7        | 6       | 5       | 4       | 3       | 2       | 1       | 0        |

|----------|---------|---------|---------|---------|---------|---------|----------|

| Reserved | MP3_CON | SYS_CON | DMA_CON | NOR_CON | DRM_CON | MMC_CON | NAND_CON |

Writing 1 to each bit disables clock supply into corresponding block and results in power down of corresponding block.

MP3\_CON: This bit is used to MP3 block power control.

0: No action.

1 : MP3 block power down.

**SYS\_CON**: This bit is used to system block power control.

0 : No action.

1 : System block power down.

$\textbf{DMA\_CON}:$  This bit is used to DMA block power control.

0 : No action.

1 : DMA block power down.

**NOR\_CON**: This bit is used to NOR flash block power control.

0 : No action.

1 : NOR flash block power down.

## NX5850 Digital Audio SoC

# **Preliminary**

$\textbf{DRM\_CON}:$  This bit is used to DRM block power control.

$0: \ No \ action.$

1 : DRM block power down.

$\mathbf{MMC\_CON}$  : This bit is used to MMC block power control.

0 : No action.

1 : MMC block power down.

$\textbf{NAND\_CON}:$  This bit is used to NAND block power control.

0 : No action.

1 : NAND block power down.

# 9. USB Controller

#### 9. USB Controller

NX5850 has the USB2.0 Full Speed function controller and the host controller which is compatible with OHCI Rev 1.0 specification. These two controllers can't be used at the same time and if one is in working, the other gets stopping.

#### 9.1. USB2.0 Full Speed Function Controller

The USB Full-Speed Function Controller consists of three end-points and each of endpoints is capable of handling the bulk, the interrupt and the isochronous data transfers at the baud rate of 12 Mbps. The endpoints can be handled by the 8051 on NX5850. The automatic data retry, the data toggle and the power management functions such as suspend and resume are all supported.

The serial information is transmitted by the USB interface containing layers of communication protocols, the most basic of which are fields. The core fields include: sync, packet identifier, address, endpoint, frame number, data, and CRC fields. Fields are used to produce packets. Depending on the function of the packet, the different combination and a number of fields are used. Packet types include: token, start of frame, data, and handshake packets. Packets are then assembled into groups to produce frames. These frames or transactions fall into four groups: bulk, control, interrupt, and isochronous. Endpoint 0, by default, is used only to communicate control transactions to configure the USB controller after it is reset or hooked up (physically connected to an active USB host or hub). Endpoint 0's responsibilities include: connection, address assignment, endpoint configuration, bus enumeration, and disconnect. Endpoint 1 is used to perform bulk OUT data transactions and receiving data from the USB host; endpoint 2 is used to perform bulk IN data transactions and transmitting data to the USB host and vice versa.

The UDC(USB Device Controller) uses two separate FIFOs to buffer incoming and outgoing data to or from the host(128-entry x 8-bit for transmitting and another 128-entry x 8-bit for receiving). The FIFOs can be filled or emptied either by the DMA or the CPU, with service requests being signaled when either FIFO is Half-Full or Empty. Interrupts are signaled when the receive FIFO experiences an overrun and the transmit FIFO experiences an under-run. The control endpoint 0 has an additional 64-entry x 8-bit FIFO that can only be read or written by processor reads and writes.

The external pins dedicated to this interface are UDC+(USB DP, Pin 8) and UDC-(USB DM, Pin 9). The USB protocol uses differential signaling between the two pins for half-duplex data transmission. A 1.5-Kohm pull-up resistor is required to be connected to the USB cable D+ signal to pull the UDC+ pin high when not driven. This signifies the UDC is a high-speed, 12-Mbps device and provides the correct polarity for data transmission. Using differential signaling allows multiple states to be transmitted on the serial bus. These states are combined to transmit data as well as various bus conditions, including: idle, resume, start of packet, end of packet, disconnect, connect, and reset.

#### 9.1.1. Operation

Following a reset of NX5850 or whenever the USB controller is attached to a USB bus, all endpoints are automatically configured by the core and the core is forced to use the USB default address of zero. The host then assigns NX5850 a unique address. At this point, the USB controller is under the host's control and responds to its commands that are transmitted to endpoint 0 using control transactions. Endpoint 1 is used to perform bulk OUT data transactions, receiving data from the USB host, and endpoint 2 bulk IN data transactions, transmitting data to the USB host.

#### 9.1.2. Signaling Levels

USB uses differential signaling to encode data and to communicate various bus conditions. The USB specification refers to the J and K data states to differentiate between high- and low-speed transmissions. Because the UDC supports only 12-Mbps transmission, references are made only to actual data state 0 and actual data state 1.

Four distinct states are represented using differential data by decoding the polarity of the UDC+ and UDC-pins. Two of the four states are used to represent data. A one is represented when UDC+ is high and UDC-is low; a zero is represented when UDC+ is low and UDC- is high. The remaining two states and pairings of the four encoding are further decoded to represent the current state of the USB bus. Table 32. shows how seven different bus states are represented using differential signaling.

Hosts and hubs have pull-down resistors on both the D+ and D- lines. When a device is not attached to the cable, the pull-down resistors cause D+ and D- to be pulled down below the single-ended low threshold of the best or bub. This creates a state called single ended zero (SEO)

| Table 21. 03b bus signal | able 21. 03b bus signal level description in according to current status                                                                                        |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bus State                | UDC+/UDC- Signal Levels                                                                                                                                         |  |  |  |  |  |

| Idle                     | UDC+ high, UDC- low (same as 1)                                                                                                                                 |  |  |  |  |  |

| Resume                   | UDC+ low, UDC- high (same as 0)                                                                                                                                 |  |  |  |  |  |

| Start of Packet          | Transition from Idle to Resume                                                                                                                                  |  |  |  |  |  |

| End of Packet            | UDC+ and UDC- low for 2-bit times followed by an idle for 2-bit time.                                                                                           |  |  |  |  |  |

| Disconnect               | UDC+ and UDC- below single-ended low threshold for more than 2.5 usec. (Disconnect is a static bus condition that result no devices is plugged-into a hub port) |  |  |  |  |  |

| Connect                  | UDC+ OR UDC- high for more than 2.5 usec.                                                                                                                       |  |  |  |  |  |

| Reset                    | UDC+ AND UDC- low for more than 2.5 usec. (Reset is driven by the                                                                                               |  |  |  |  |  |

Table 21. USB bus signal level description in according to current status

A disconnect is detected by the host when an SEO persists for more than 2.5 usec (30-bit times). When the UDC is connected to the USB cable, the pull-up resistor on the UDC+ pin causes D+ to be pulled above the single-ended high threshold level. After 2.5 usec elapse, the host detects a connect.

After this point, the bus is in the idle state because UDC+ is high and UDC- is low. A start of packet is signaled by transitioning the bus from the idle to the resume state (a 1 to 0 transition). The beginning of each USB packet begins with a sync field, which starts with the 1-to-0 transition.

After the packet data has been transferred, an end of packet is signaled by pulling both UDC+ and UDC- low for 2-bit times, followed by an idle for 1-bit time. If the idle persists for more than 3 msec, the UDC enters suspend mode and it is placed in low-power mode. The UDC can be awakened from the suspend state by the host by switching the bus to the resume state via normal bus activity, or by signaling a reset. Under normal operating conditions, the host ensures that devices do not enter the suspend state by periodically signaling an end of packet (EOP).

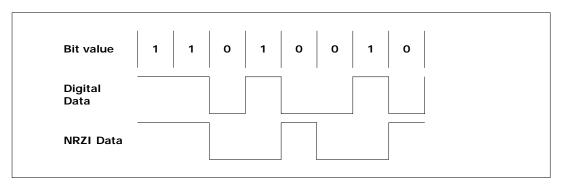

#### 9.1.3. Bit Encoding

The USB uses non-return-to-zero inverted (NRZI) to encode individual bits. Both the clock and the data are encoded and transmitted within the same signal. Instead of representing data by controlling the state of the signal, transitions are used. A zero is represented by a transition, and a one is represented by no transition (this produces the data).

Each time a zero occurs, the receiver logic synchronized the baud clock to the incoming data (this produces the clock). To ensure the receiver is periodically synchronized, any time six consecutive ones are detected in the serial bit stream, a zero is automatically inserted by the transmitter. This procedure is known as "Bit stuffing". The receiver logic, in turn, automatically detects stuffed bits and removes them from the incoming data. Bit stuffing causes a transition on the incoming signal at least once every seven bit-times to guarantee baud clock lock. Bit stuffing is enabled for an entire packet beginning when the start of packet is detected until the end of packet is detected (enabled during the sync field all the way through the CRC field). Figure 11. shows the NRZI encoding of the data byte 0b1101 0010.

Figure 8. NRZI bit encoding example

#### 9.1.4. Field Formats

Individual bits are assembled into groups called fields. Fields are used to construct packets and packets are used to construct frames or transactions. The seven USB field types include: sync, packet identifier, address, endpoint, frame number, data, and CRC fields.

Sync is preceded by the idle state on the USB bus and is always the first field of every packet. The first bit of a sync field signals the start of packet (SOP) to the UDC or host. Sync is 8 bits wide and consists of seven zeros followed by a one (0x80).

The packet identifier (PID) is 1 byte wide and always follows the sync field. The first 4 bits contain an encoded value that represents packet type (token, data, handshake and special), packet format, and type of error detection. The last four bits contain a check field that ensures the PID is transmitted without errors. The check field is generated by performing a ones complement of the PID. The UDC automatically XORs the PID and check field and takes the appropriate action (as prescribed by the USB standard) if the result does not contain all ones, indicating an error has occurred in transmission.

The UDC's three endpoints are accessed using the address and endpoint fields. The address field contains 7 bits and permits 128 unique devices to be placed on the USB. After NX5850 is reset, or a reset is signaled via the USB bus, the UDC (and all other 127 possible devices) is assigned the default address of zero. The host is then responsible for assigning unique addresses for each device on the bus. This is performed in the enumeration process one device at a time. Once the host assigns the UDC an address, it responds only to transactions addressed to it. The address field is transmitted in every packet and follows the PID field.

When the UDC detects that a packet is addressed to it, the endpoint field is used to determine which of the UDC's three endpoints are being addressed. The endpoint field is 4 bits. However, only the encoding for endpoints 0 through 2 is allowed. The endpoint field follows the address field. Table 20. shows the valid values for the endpoint field. The frame number is an 11-bit field that is incremented by the host each time a frame is transmitted. When it reaches its maximum value of 2047 (0x7FF), it rolls over. It is transmitted in the start of frame (SOF) packet, which is output by the host in 1 msec intervals. The frame number field is used only by device controllers to control isochronous transfers, and therefore, does not affect the UDC. Data fields are used to transmit the bulk data between the host and the UDC. A data field is made up of 0 to 1023 bytes. Each byte is transmitted LSB first.

Table 22. Endpoint field addressing

| Endpoint Field Value | UDC Endpoint Selected |

|----------------------|-----------------------|

| 0000                 | Endpoint 0            |

| 0001                 | Endpoint 1            |

| 0010                 | Endpoint 2            |

| 0011                 | Invalid               |

| 01xx                 | Invalid               |

| 10xx                 | Invalid               |

| 11xx                 | Invalid               |

Cyclic redundancy check fields are used to detect errors introduced during transmission of token and data packets, and is applied to all the fields in the packet except the PID field (recall the PID contains its own 4-bit ones complement check field for error detection). Token packets use a 5-bit CRC (x 5 + x 2 + 1) and data packets use a 16-bit CRC (x 16 + x 15 + x 2 + 1). For both CRCs, the checker is reset to all ones at the start of each packet.

#### 9.1.5. Packet Formats

USB supports four packet types: token, data, handshake, and special. A token packet is placed at the beginning of a frame and is used to identify OUT, IN, SOF, and SETUP transactions. OUT and IN frames are used to transfer data, SOF packets are used to time isochronous transactions, and SETUP packets are used for control transfers to configure endpoints. A token packet consists of a sync, a PID, an address, an endpoint, and a CRC5 field. For OUT and SETUP transactions, the address and endpoint fields are used to select which UDC endpoint is to receive the data, and for an IN transaction, which endpoint must transmit data.

Table 23. IN, OUT, and SETUP token packet format

| 8 bits | 8 bits | 7 bits  | 4 bits   | 5 bits |

|--------|--------|---------|----------|--------|

| Sync   | PID    | Address | Endpoint | CRC5   |

A start of frame (SOF) is a special type of token packet that is issued by the host once every 1 msec. SOF packets consist of a sync, a PID, a frame number (which is incremented after each frame is transmitted), and a CRC5 field, as shown in Table 22. Even though the UDC on the Scorpio does not make use of the frame number field, the presence of SOF packets every 1ms will prevent the UDC from going into suspend mode.

Table 24. SOF token packet format

| 8 bits | 8 bits | 11 bits      | 5 bits |

|--------|--------|--------------|--------|

| Sync   | PID    | Frame Number | CRC5   |

Data packets follow token packets, and are used to transmit data between the host and UDC. There are two types of data packets as specified by the PID: DATAO and DATA1. These two types are used to provide a mechanism to guarantee data sequence synchronization between the transmitter and receiver across multiple transactions. During the handshake phase, both communicate and agree which data token type to transmit first. For each subsequent packet transmitted, the data packet type is toggled (DATAO, DATA1, DATAO, and so on). A data packet consists of a sync, a PID, from 0 - 256 bytes of data, and a CRC16 field, as shown in Table 23.

Table 25. Data packet format

| 8 bits | 8 bits | 0 – 256 bytes | 16 bits |

|--------|--------|---------------|---------|

| Sync   | PID    | Data          | CRC16   |

Handshake packets consist of only a sync and a PID. Handshake packets do not contain a CRC because the PID contains its own check field. They are used to report data transaction status, including whether data was successfully received, flow control, and stall conditions. Only transactions that support flow control can return handshakes. The three types of handshake packets are: ACK, NAK, and STALL. ACK indicates that a data packet was received without bit stuffing, CRC, or PID check errors. NAK indicates that the UDC was unable to accept data from the host or it has no data to transmit. NAK is also used by endpoint 1 to indicate no interrupts are pending. STALL indicates that the UDC is unable to transmit or receive data, and requires host intervention to clear the stall condition. Bit stuffing, CRC, and PID errors are signaled by the receiving unit by omitting a handshake packet. Table 24. shows the format of a handshake packet.

Table 26. Handshake packet format

| 8 bits | 8 bits |

|--------|--------|

| Sync   | PID    |

#### 9.1.6. Transaction Formats